Hosted by: School of Engineering, Boole Centre for Research in Informatics, Claude Shannon Institute, School of Mathematical Sciences

Date: September 1st & 2nd, 2015

Venue: Room G02, Brookfield Health Sciences Complex, University College Cork(UCC) campus

Sponsored by: FP7/i-RISC, UCC, SFI, BCRI, MCCI, Tyndall, Analog Devices, Synopsys, Qualcomm, Intel

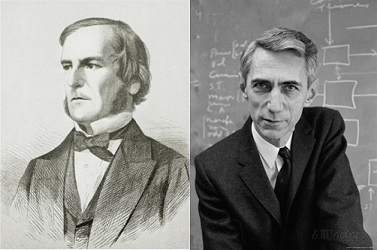

George Boole’s Bicentenary Celebrations

In 2015, University College Cork celebrates the bicentenary of George Boole, 1815-64. Born in Lincoln, Boole was a mathematical genius who was largely self-taught. His appointment as the first Professor of Mathematics at this college in 1849 provided the opportunity to develop his most important work, An Investigation of the Laws of Thought.

Boole is a pivotal figure who can be described as the ‘father of the information age’. His invention of Boolean algebra and symbolic logic pioneered a new mathematics. His legacy surrounds us everywhere, in the computers, information storage and retrieval, electronic circuits and controls that support life, learning and communications in the 21st century.

Workshop Purpose

The i-RISC Workshop addresses the problem of reliable computing with unreliable components, which is a crucial issue for the long-term development of computing technology. The Workshop main goal is to explore the synergistic utilization of information theory and coding techniques, traditionally utilized to improve the reliability of communication systems, and circuit and system theory and design techniques in order to create reliable/predictable hardware. The aim is to enable the development of innovative fault-tolerant solutions at both circuit- and system-level, combining mathematical models, algorithms, and techniques that are fundamentally rooted in Shannon’s theory of information and Boole’s theory of logic.

Context

The ongoing miniaturization of data processing and storage devices and the imperative of low-energy consumption can only be sustained through low-powered components. However, lower supply voltages combined with variations in technological process of emerging nanoelectronic devices make them inherently unreliable. As a consequence, the nanoscale integration of chips built out of unreliable components has emerged as one of the most critical challenges for the next-generation electronic circuit design. To make such nanoscale integration economically viable, new solutions for efficient and fault-tolerant data processing and storage must be investigated.

i-RISC Workshop Local Organizing Committee

Dr. Emanuel Popovici, School of Engineering-Electrical and Electronic

Dr. Liam Marnane, School of Engineering-Electrical and Electronic

Dr. Kevin McCarthy, School of Engineering-Electrical and Electronic

i-RISC Workshop Technical Committee

Sorin Cotofana, TU Delft, Nederlands

Bane Vasic, University of Arizona, USA

Valentin Savin, CEA-Leti (co-chair), France

Alexandru Amaricai, University Politehnica Timisoara, Romania

Predrag Ivanis, University of Belgrade, Serbia

David Declerq, ENSEA Paris, France

Goran Djordjevic, University of Nis, Serbia

Emanuel Popovici, University College Cork, Ireland