# Timing Error Analysis of Flooded LDPC Decoders

Alexandru Amaricai, Valentin Savin, Oana Boncalo, Nicoleta Cucu-Laurenciu, Joyan Chen, Sorin Cotofana

#### FP7-ICT / FET-OPEN - 309129 / i-RISC Innovative Reliable Chip Designs from Low-Powered Unreliable Components

- Related work

- Motivation

- LDPC decoder architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

### Related work

### Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

### **Related Work**

Theoretical analysis of faulty LDPC decoders

- C/C++ or Matlab LDPC decoder models

- Simple probabilistic errors

- Wide range of decoding algorithms

- One step majority logic decoding [Chilappagari06]

- Gallagher-A decoding [Varshney11]

- Gallagher-B decoding [Yazdi13]

- Min–Sum decoding i–Risc project

- FAID decoding i–Risc project

### Related work

### Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

### Motivation

- Decoding algorithm #Decoder implementation

- Wide range of architectural and implementation choices for the same decoding algorithm

- Ex: parallelism degree at decoder level, parallelism degree at computational node level, message storage, pipelining, etc

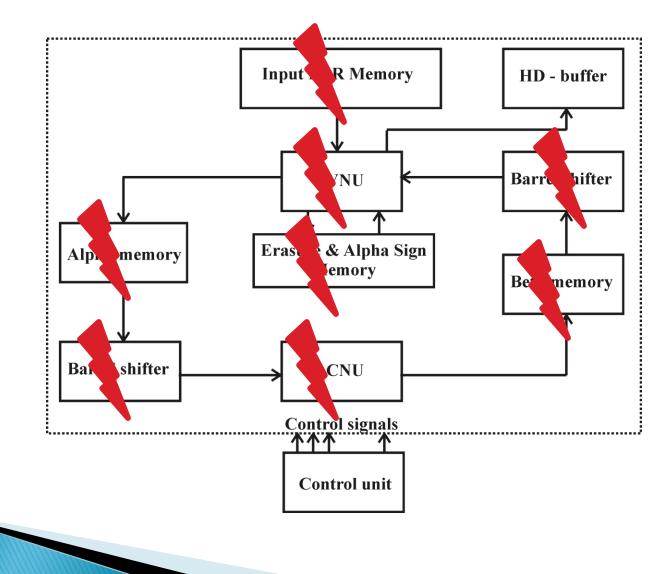

- Influence of probabilistic errors on decoding performance of a LDPC decoder architecture

- Probabilistic timing errors

- Fault map highly depend on implementation choices

- Error probability depends on the delay associated to each path

### Motivation

### Contributions

- The analysis is performed on an RTL description of an LDPC decoding architecture

- Accurate timing error modeling for sub-powered LDPC decoder

- Conclusion

- Estimate of potential overclocking applicable to an LDPC decoder architecture

- Throughput increase via overclocking

- Related work

- Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

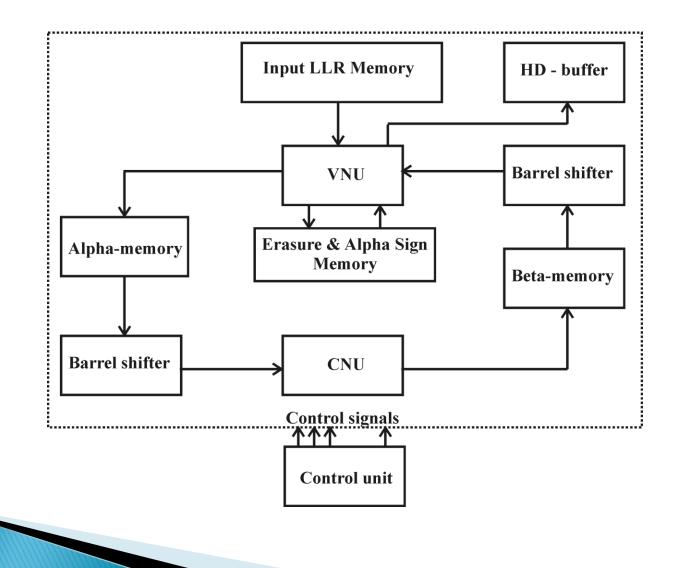

### LDPC decoder parameters

- (3,6)-regular QC-LDPC code

- 1296 bits codeword

- Circulant size 54

- Flooded decoding

- Early termination

- Decoding algorithms:

- MS, SCMS (4,6) quantization

- FAID 3 bits quantization

- Serial processing messages at computational node (VNU/CNU) level

- Reduction in memory access ports

- Parallel processing at B matrix row/column level

- Increase in throughput

- B matrix rows and columns are processed in serial

- Related work

- Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

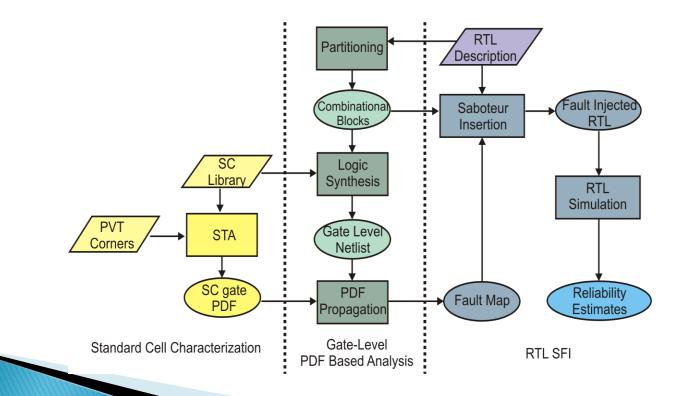

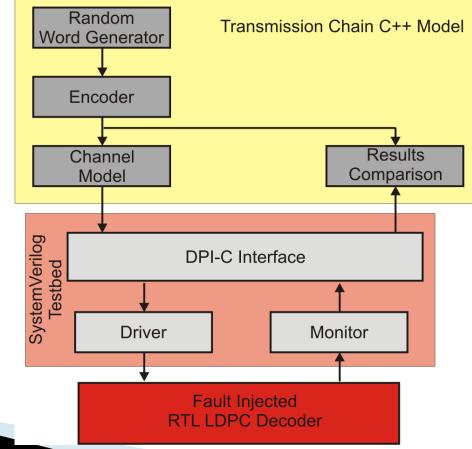

## Evaluation Framework & Methodology

- Three layer evaluation methodology

- Probabilities associated to each combinational primary output (PO) dependent on the PO delay

## Evaluation Framework & Methodology

Average Probabilities for Considered Blocks

| Clock<br>Period<br>(ns) | Mem  | BS   | MS/<br>SCMS<br>CNU | MS<br>VNU | SCMS<br>VNU | FAID<br>CNU | FAID<br>VNU |

|-------------------------|------|------|--------------------|-----------|-------------|-------------|-------------|

| 5.50                    | 0.00 | 0.00 | 1.28               | 0.00      | 0.00        | 9.70        | 0.00        |

|                         | E+00 | E+00 | E-10               | E+00      | E+00        | E-11        | E+00        |

| 4.00                    | 0.00 | 0.00 | 3.51               | 3.14      | 2.47        | 2.66        | 2.26        |

|                         | E+00 | E+00 | E-07               | E-08      | E-08        | E-07        | E-09        |

| 2.50                    | 9.64 | 2.79 | 6.05               | 1.92      | 1.51        | 4.58        | 4.61        |

|                         | E-07 | E-06 | E-04               | E-04      | E-04        | E-04        | E-05        |

| 2.20                    | 1.28 | 2.71 | 2.33               | 9.94      | 7.81        | 1.76        | 3.12        |

|                         | E-05 | E-05 | E-03               | E-04      | E-04        | E-03        | E-04        |

| 1.90                    | 1.60 | 2.62 | 8.13               | 4.80      | 3.77        | 6.18        | 1.98        |

|                         | E-04 | E-04 | E-03               | E-03      | E-03        | E-03        | E-03        |

| 1.70                    | 8.28 | 1.17 | 1.75               | 1.30      | 1.02        | 1.33        | 6.48        |

|                         | E-04 | E-03 | E-02               | E-02      | E-02        | E-02        | E-03        |

## Evaluation Framework & Methodology

### **Evaluation Framework**

Comparison with encoded data rather than comparison with correct LDPC decoder

- Related work

- Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

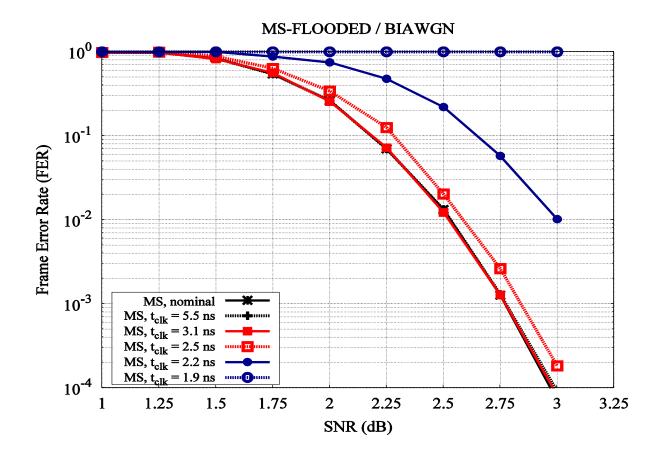

### **MS Under BIAWGN**

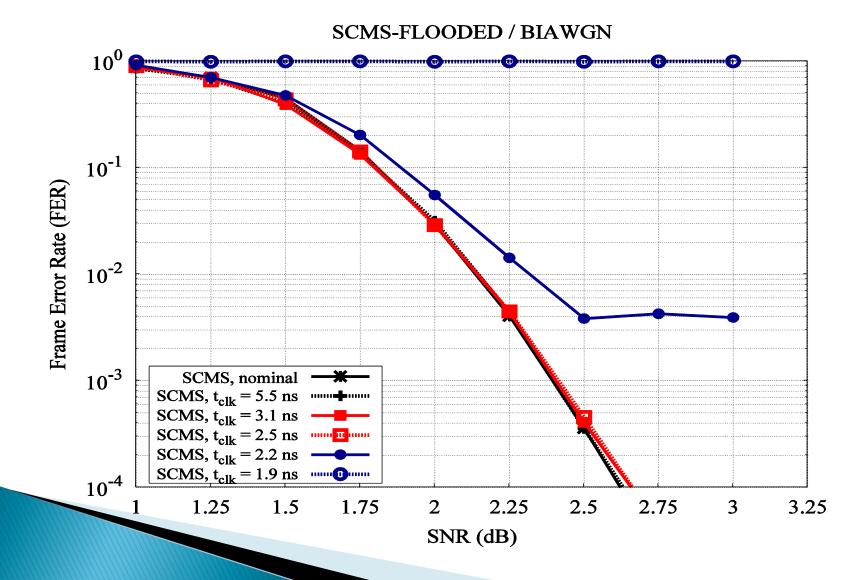

## SCMS Under BIAWGN Faulty additional memories

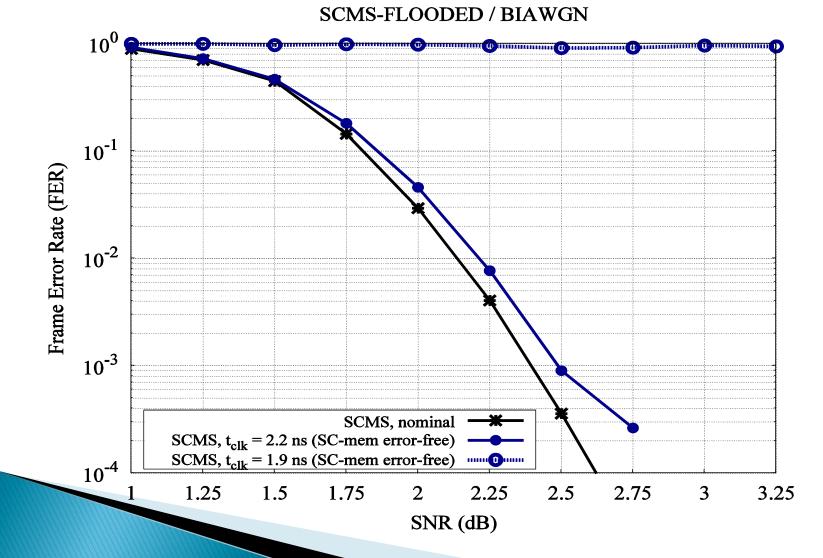

#### SCMS Under BIAWGN Non-faulty additional memories

- Related work

- Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

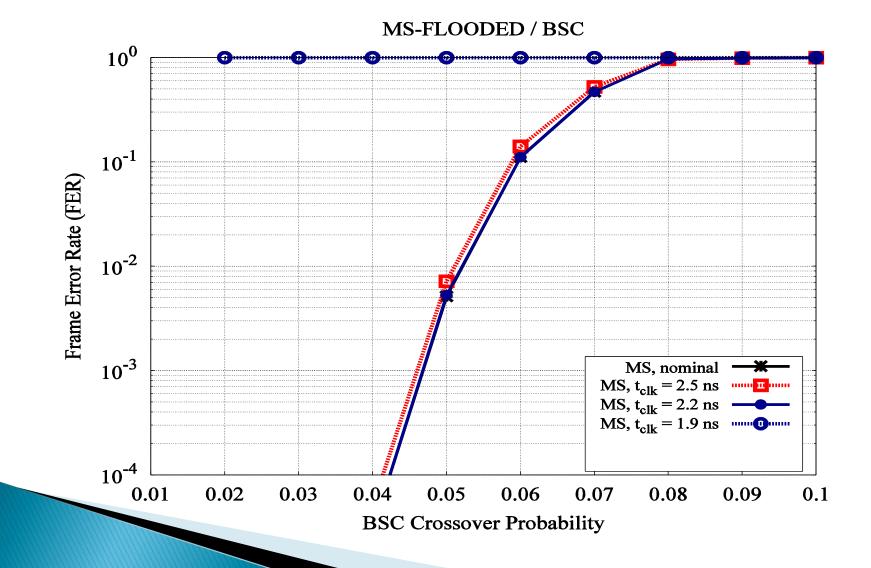

### **MS Under BSC** • Gain factor 3

MS-FLOODED / BSC 10<sup>0</sup> ······ 10<sup>-1</sup> Frame Error Rate (FER) 10<sup>-2</sup>  $t_{clk} \ge 2.5$ 10<sup>-3</sup> MS, nominal MS,  $t_{clk} = 5.5 \text{ ns}$ MS,  $t_{clk} = 3.1 \text{ ns}$ MS,  $t_{clk} = 2.5 \text{ ns}$ MS,  $t_{clk} = 2.2 \text{ ns}$ MS,  $t_{clk} = 1.9$  ns 7 10<sup>-4</sup> 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

**BSC Crossover Probability**

### **MS Under BSC** • Gain factor 4

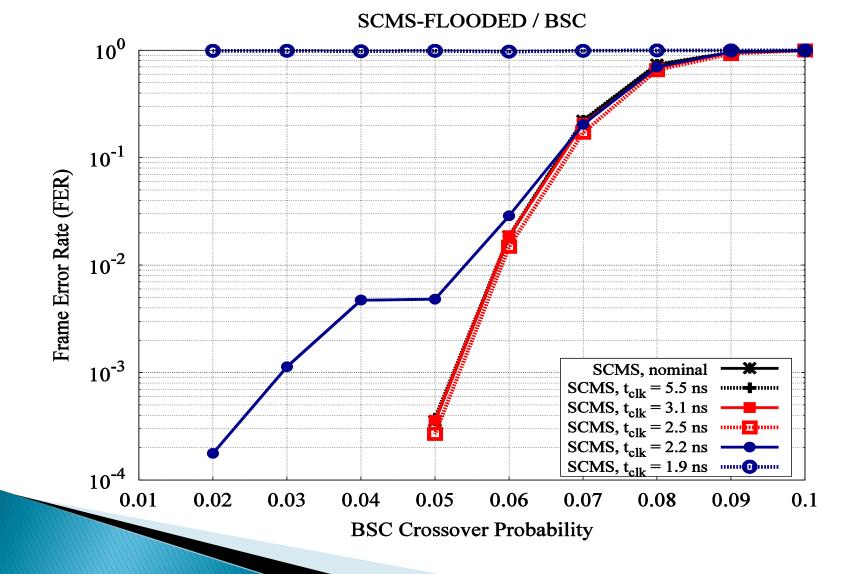

### SCMS Under BSC • Faulty additional memories

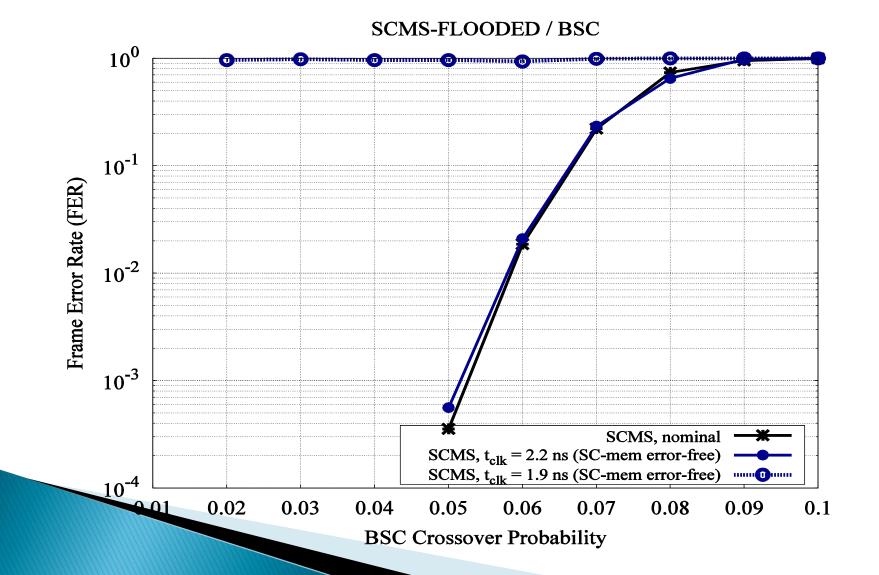

#### SCMS Under BSC Non-faulty additional memories

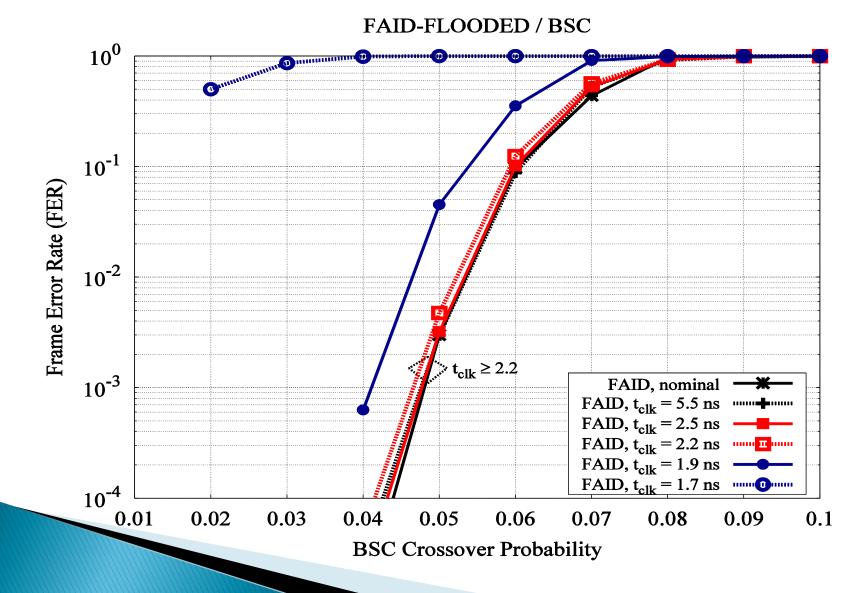

### FAID Under BSC

- Related work

- Motivation

- LDPC decoding architecture

- Evaluation framework & methodology

- Faulty decoders under BIAWGN

- Faulty decoders under BSC

- Conclusions

### Conclusions

- LDPC decoder capability of correcting errors in their internal data-path

- Influence of the errors in the two additional memories of SCMS

- Influence of gain factor in MS for BSC

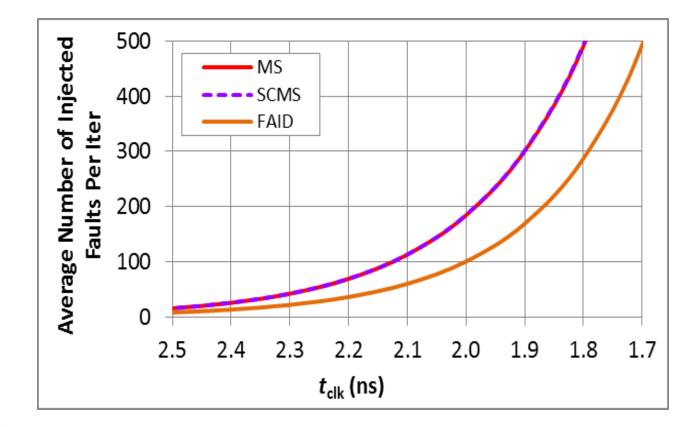

- FAID ability to withstand higher clock frequencies (it has lower fault probabilities)

- Throughput increase via overclocking

- 70%-150% increase by overclocking

### Thank You